УДК 681.323

# МУЛЬТИПРОЦЕССОРНЫЙ МОДУЛЬ НА ОСНОВЕ ВЫСОКОПРОИЗВОДИТЕЛЬНЫХ ПРОЦЕССОРОВ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ<sup>1</sup>

Букварев E.A., научный сотрудник кафедры информационных радиосистем Нижегородского государственного технического университета им. Р. Е. Алексеева, e-mail: bukvarev@rambler.ru;

Kузин A.A., доцент кафедры информационных радиосистем Нижегородского государственного технического университета им. Р. Е. Алексеева, e-mail: kuzin\_alex@nntu.nnov.ru;

Приблудова Е.Н., кандидат технических наук, доцент кафедры информационных радиосистем Нижегородского государственного технического университета им. Р.Е. Алексеева, e-mail: pribludova@nntu.nnov.ru; Рындык А.Г., доктор технических наук, профессор, заведующий кафедрой информационных радиосистем Нижегородского государственного технического университета им. Р. Е. Алексеева, e-mail: a ryndyk@nntu.nnov.ru.

### MULTIPROCESSOR MODULE BASED ON *HIGH-PERFORMANCE* PROCESSORS OF DIGITAL SIGNAL PROCESSING

### Bukvarev E.A., Kuzin A.A., Pribludova E.N., Ryndyk A.G.

In this paper multiprocessor module structure on basis of high-performance processor of digital signal processing designed and producible by JSC PKK Milandr is considered. Start initialization of multiprocessor system is described, some design features are considered, configuration and appearance of the integrated module are shown. Characteristics of capability and assessment of power consumption are provided.

The developed integrated module is intended for use in stationary and mobile systems of high-performance digital signal processing.

Key words: digital processing, signal processor, multiprocessor system, integrated module.

**Ключевые слова:** цифровая обработка, сигнальный процессор, мультипроцессорная система, интегрированный модуль.

### Введение

В настоящее время весьма перспективна концепция реконфигурируемых многопроцессорных вычислителей, предоставляющая возможность пользователю адаптировать архитектуру вычислительной системы под структуру решаемой задачи.

По мнению многих разработчиков, оптимальными высокопроизводительными системами цифровой обработки являются конфигурации смешанного типа, объединяющие сигнальные процессоры, аппаратные ускорители и программируемую логику [1].

Однако, существуют интенсивные вычислительные алгоритмы, которые не могут быть хорошо реализованы на программируемой логике. Такие проблемно-ориентированные задачи требуют много управляющих ресурсов и обладают сложной логикой принятия решений, что делает предпочтительной их программную реализацию [1].

Рассмотрена структура многопроцессорного модуля на основе высокопроизводительных процессоров цифровой обработки сигналов, разработанных и производимых ЗАО «ПКК Миландр». Описана начальная инициализация мультипроцессорной системы, рассмотрены некоторые конструктивные особенности, показаны компоновка и внешний вид интегрированного модуля. Приведены характеристики производительности и оценки потребляемой мощности.

Разработанный интегрированный модуль предназначен для использования в системах высокопроизводительной цифровой обработки сигналов гражданского и оборонного назначения, как в стационарных, так и в мобильных.

Отсутствие отечественных микросхем специализированной программируемой логики для ЦОС смещает акцент в пользу развития распределенных многопроцессорных топологий на основе DSP-процессоров.

#### Постановка задачи

Разработка отечественного суперскалярного DSPпроцессора [2, 3] позволила проектировать на его основе масштабируемые высокопроизводительные системы обработки данных.

С учетом предполагаемой сферы применения — от традиционной цифровой обработки в радиолокации, радиосвязи, гидроакустике и т.п. до транспортных, авиационно-космических и энергетических систем, вычислитель должен предоставлять пользователю возможность выбора вычислительной мощности от 4 до 20 процессоров в модуле, быть относительно компактным и устойчивым к внешним воздействиям.

<sup>&</sup>lt;sup>1</sup> Работа выполнена при поддержке Министерства образования и науки РФ в рамках договора № 02.G25.31.0061 от 12 февраля 2013 года (в соответствии с Постановлением Правительства Российской Федерации от 9 апреля 2010 г. № 218).

Вычислительный модуль должен иметь связь с целевым устройством (ЦУ), совместно с которым используется, по стандартным интерфейсам. Эта связь позволяет выполнять конфигурирование, загрузку задач и данных и управление вычислениями. Наличие стандартных интерфейсов дает возможность собирать из таких интегрированных модулей (ИМ) системы более высокой производительности. В качестве стандартных интерфейсов ИМ заданы Ethernet и PCI-Express.

### Структура интегрированного модуля

При проектировании структуры интегрированного модуля на основе высокопроизводительных процессоров цифровой обработки сигналов (ВПЦОС) рассматривались различные варианты логической организации мультипроцессорного вычислителя и различные варианты конструктивного исполнения.

Существенное влияние на логическую структуру вычислителя оказали некоторые особенности применяемого ВПЦОС [2]: наличие встроенного в контроллер внешней шины арбитра и наличие четырех высокоскоростных полнодуплексных последовательных LVDS-портов обмена (LINK-портов).

Встроенный арбитраж шины позволяет без дополнительной управляющей логики объединять до четырех процессоров в кластер в виде системы с общей (кластерной или мультипроцессорной) шиной. В этом случае каждый из процессоров имеет доступ к внутренним ресурсам (внутренней памяти и регистрам) любого другого ВПЦОС [2, 3]. К кластерной шине подключается внешняя разделяемая память (как правило, синхронная динамическая память SDRAM).

Внешние LINK-порты допускают организацию произвольных информационных связей между процессорами, что эффективно при реализации потоковых алгоритмов.

Известно, что наиболее эффективной является такая система маршрутизации информационных потоков в мультипроцессорной системе, которая обеспечивает возможность соединения любого процессора с любым другим.

В процессе проектирования от такой системы коммутируемых соединений отказались на основании следующих соображений:

- внутри процессорного кластера соединения по LINK-портам носят вспомогательный характер, основной обмен между процессорами производится по кластерной шине;

- порты ВПЦОС выполнены по LVDS стандарту, что при четырехразрядном полнодуплексном обмене требует 24 проводника на каждый порт, а это, в свою очередь, сильно усложняет систему программируемой коммутации;

- коммутатор требует дополнительных управляющих ресурсов с частотой передачи данных до 800 МГц, что является непростой задачей при ориентировании на отечественную элементную базу.

Таким образом, логическая структура интегрированного модуля представляет собой гетерогенную вычислительную систему, в которой четырехпроцессорные кластеры связаны по LINK-портам при помощи системы некоммутируемых (постоянных) связей. Интегрированный модуль может содержать от одного до пяти кластеров.

Рассматривалось несколько вариантов компоновки интегрированного модуля, в частности, исполнение ИМ в виде одноплатного варианта. Вариант оказался трудно реализуемым из-за большого размера платы (по оценке 300 × 415 мм) и, как следствие, сложности трассировки, изготовления, монтажа и отладки. Кроме того, данный вариант не обладает свойством масштабируемости.

Вторым вариантом компоновки рассматривалась реализация ИМ в виде блока (крейта), содержащего набор кластеров, выполненных в виде отдельных ячеек. В этом случае источник вторичного питания выполняется отдельным конструктивным модулем, а связи между ячей-ками обеспечиваются объединительной платой блока. Основные недостатки этого варианта — плохие массогабаритные характеристики и проблема качественного изготовления объединительной платы для высокочастотных сигналов LINK-портов.

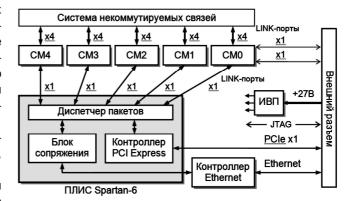

Третий вариант компоновки ИМ, который был принят к дальнейшей реализации, — базовая (несущая плата) с устанавливаемыми на ней субмодулями (мезонинами). Субмодуль (СМ) — функционально законченный четырехпроцессорный кластер. Структура ИМ показана на рис. 1.

Рис.1. Структура интегрированного модуля

Базовая плата ИМ допускает установку от одного до пяти субмодулей СМО — СМ4, обмен между которыми обеспечивается системой некоммутируемых связей. Межмодульный обмен — полнодуплексной четырехразрядный с тактовой частотой до 400 МГц, что в режиме DDR (Double Data Rate — двойная скорость передачи данных) позволяет передавать до 400 МБайт/с по каждому LINK-порту.

Связь между субмодулями и внешними интерфейсами выполнена на ПЛИС Spartan 6, контроллер Ethernet – внешний (стандарт Fast Ethernet IEEE 802.3u 100BaseTX), контроллер PCI Express – встроенный (стандарт PCI SIG PCI Express External Cable Specification 1.0 2.5 Gbps full duplex). Диспетчер пакетов, входящий в состав ПЛИС, связан с LINK-портами субмодулей – на каждом субмодуле два одноразрядных порта с частотой синхронизации 100 МГц (скорость передачи по каждому порту 25 МБайт/с).

Внешние интерфейсы и два LINK-порта субмодуля СМ0 используют высокочастотную часть внешнего разъема, предназначенную для передачи дифференциальных сигналов.

Другая часть внешнего разъема предназначена для подачи питания и подключения относительно низкочастотных JTAG-интерфейсов. Отладочные JTAG-интерфейсы на каждом СМ образуют цепочку, охватывающую четыре ВПЦОС, с каждого субмодуля JTAG-цепочка выводится на внешний разъем.

На базовой плате расположены несколько источников вторичного питания (ИВП). Первую ступень питания образует DC/DC преобразователь, формирующий напряжение +5 В с током нагрузки до 24 А, входное напряжение преобразователя от 16 до 40 В.

Вторая ступень питания из +5 В формирует напряжение +3,3 В на субмодули и вспомогательные напряжения питания для компонентов базовой платы.

На рис. 1 не показаны схемы буферизации внешних интерфейсов и JTAG, так же не показан контроллер питания, обеспечивающий последовательное включение питания субмодулей.

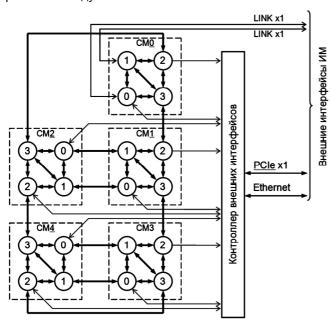

На рис. 2 показаны межпроцессорные связи интегрированного модуля.

Рис. 2. Структура последовательных межпроцессорных связей ИМ (LINK-портов)

Как видно из рис. 2, внутри субмодуля не удалось обеспечить связь «каждый с каждым», поскольку часть LINK-портов (у ВПЦОС 0 и 2) используется для информационного обмена с контроллером внешних интерфейсов.

Ограниченное количество межкластерных связей может снизить производительность системы в целом изза необходимости использовать некоторые процессорные узлы для транзита данных. Однако, разработанный ВПЦОС поддерживает DMA передачи между LINK-портами (LINK to LINK DMA) напрямую без буферизации во внутренней памяти, чем выгодно отличается от ADSP-TS201.

### Начальная инициализация интегрированного модуля

Начальная инициализация ИМ выполняется в два этапа: последовательное включение питания и загрузка по всем процессорам некоторого базового программного обеспечения (ядра операционной системы).

Последовательность включения питания выглядит следующим образом:

- на интегрированный модуль подается внешнее напряжение +27 В;

- напряжение +5 В, а затем вспомогательные напряжения источников питания базовой платы достигают номинальных значений;

- запускается процесс конфигурирования ПЛИС контроллера внешних интерфейсов Spartan 6 из конфигурационной Flash-памяти:

- по завершении конфигурирования ПЛИС контроллер питания на CPLD XA8572XL начинает последовательное включение субмодулей, формируя управляющий сигнал PWR\_ON (включить питание) на соответствующий субмодуль и анализируя ответный сигнал PWR GOOD (питание в норме) от субмодуля;

- если по истечении определенного времени ответный сигнал не активируется, модуль считается неисправным;

- после включения питания последнего субмодуля СМ4, контроллер питания формирует сигнал о завершении управляющей последовательности PWR OK.

Во время включения питания ПЛИС контроллера интерфейсов удерживает в активном состоянии управляющий сигнал DSP\_RST сброса процессоров в субмодулях. По завершении включения питания сигнал DSP\_RST деактивируется, что приводит к выполнению во всех процессорах процедуры начальной загрузки.

В разработанных субмодулях используется два режима начальной загрузки — загрузка из постоянной памяти (ВПЦОС 0) и загрузка по LINK-портам (ВПЦОС 1, 2 и 3).

Режим загрузки определяется уровнем сигнала BMS во время снятия сброса процессора [2], низкий уровень BMS — загрузка из Flash-памяти, высокий — загрузка по LINK-порту.

Процессор ВПЦОС 0 загружает некоторое базовое программное обеспечение (ПО), например, ядро операционной системы. После загрузки и запуска ядра обеспечивается его копирование по LINK-порту в соседний процессор. Загрузка и запуск ПО на последнем ВПЦОС 3 приводит к формированию сигнала DSP\_LOAD, который сообщает контроллеру интерфейса о завершении загрузки ПО на процессоры.

Контроллер внешних интерфейсов предоставляет пользователю возможность индивидуального формирования сигнала DSP\_RST для субмодулей, т.е. обеспечивать независимый рестарт ПО в субмодулях, например, при зацикливании прикладной задачи.

## Конструкция и характеристики интегрированного модуля

Выбранный вариант компоновки ИМ в виде базовой платы с мезонинными модулями (до пяти мезонинов) обладает рядом проблем:

- большая площадь несущей платы;

- большое количество высокоскоростных согласованных дифференциальных линий для межмодульного обмена;

- большая рассеиваемая мощность.

Первая проблема была решена размещением мезо-

62

нинов с двух сторон печатной платы — три с одной стороны и два с другой. Напротив одного из мезонинов с другой стороны базовой платы размещены ИВП и контроллер внешних интерфейсов. Размер базовой платы при такой компоновке составил 288 × 170 мм.

Вторая проблема была решена специальным распределением сигналов высокоскоростных LINK-портов по разъемам субмодулей.

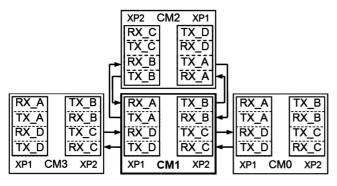

Субмодуль (например, СМ1 на рис. 2) имеет связь с соседними, расположенными на одной стороне с ним (СМ0 и СМ3), и связи с субмодулем на противоположной стороне базовой платы (СМ2). Межпроцессорные LINK-порты условно названы A, B, C и D, RX\_n и TX\_n – приемный и передающий канал соответствующего порта. Схема распределения сигналов по разъемам XP1 и XP2 субмодуля показана на рис. 3.

Из рис. З видно, что связи между соседними субмодулями минимальны, а связь с противоположным модулем (СМ2) вообще может быть выполнена в виде переходных отверстий.

Рис. 3. Распределение сигналов на разъемах LINK-портов

Третья проблема – проблема отвода тепла была решена применением внутренних теплопроводящих пластин и установкой внешнего ребристого радиатора из алюминия.

Интегрированный модуль с установленными пятью субмодулями показан на рис. 4. Следует отметить, что на рис. 4 отсутствуют элементы системы охлаждения интегрированного модуля.

Конструктивно, интегрированный модуль представляет собой моноблок с пассивным воздушным охлаждением, предназначенный для установки в целевое устройство (ЦУ) – устройство, в составе которого будет производиться эксплуатация одного или нескольких ИМ. Внешний вид модуля показан на рис. 5, размер  $300 \times 175 \times 74$  мм, масса не более 3.9 кг.

Конструктивное исполнение интегрированного модуля и результаты теплового моделирования подробно

приведены в [4]. Выбранная компоновка обладает повышенной механической прочностью и обеспечивает возможность хорошего электромагнитного экранирования, что позволяет, в принципе, вместо процессорных субмодулей устанавливать субмодули аналогового ввода/вывода.

Puc. 4. Расположение компонентов на базовой плате интегрированного модуля

Рис. 5. Внешний вид интегрированного модуля

Интегрированный модуль может иметь несколько вариантов исполнения, отличающихся количеством установленных субмодулей, а значит и характеристиками, некоторые из которых приводятся в табл. 1.

Таблица 1. Характеристики интегрированного модуля по вариантам исполнения

| Вариант исполнения | Варианты субмодулей | Кол-во субмодулей | Пиковая произв.,<br>MFLOPS | Потребляемая мощность, Вт |

|--------------------|---------------------|-------------------|----------------------------|---------------------------|

| НМРУ.466216.001    | НМРУ.466216.001-01  | 5                 | 24 000                     | 86                        |

| НМРУ.466216.001-01 | НМРУ.466216.001-01  | 4                 | 19 200                     | 71                        |

| НМРУ.466216.001-02 | НМРУ.466216.001-01  | 3                 | 14 400                     | 55                        |

| НМРУ.466216.001-03 | НМРУ.466216.001-01  | 2                 | 9 600                      | 39                        |

| НМРУ.466216.001-04 | НМРУ.466216.001-01  | 1                 | 4 800                      | 23                        |

| НМРУ.466216.001-05 | НМРУ.466216.001-02  | 1                 | 4 800                      | 23                        |

#### Заключение

Разработанный интегрированный модуль предназначен для использования в системах высокопроизводительной цифровой обработки сигналов гражданского и оборонного назначения. Модуль может применяться как в стационарных, так и в мобильных системах.

Организация внутренних и внешних связей интегрированного модуля допускает наращивание количества модулей в системе, что позволяет проектировать масштабируемые вычислители высокой производительности. Система на основе интегрированных модулей легко адаптируется для решения широкого класса задач цифровой обработки сигналов и управления в реальном времени.

Настройка (конфигурирование) как интегрированного модуля, так и системы в целом, на решение конкретной

задачи цифровой обработки выполняется с помощью специализированного программного обеспечения.

### Литература

- 1. Кравотта Р. Выбор правильных технологий обработки сигналов // Chip News. – 2007. – № 2. – C.17-20.

- 2. Сигнальный процессор со статической суперскалярной архитектурой 1967ВЦ2Ф, К1967ВЦ2Ф, К1967ВЦ2ФК. Спецификация. URL:http://milandr.ru/uploads/Products/product 294/spec 1967VC2.pdf

- 3. Мякочин Ю.О. 32-разрядный суперскалярный DSP-процессор с плавающей точкой // Компоненты и технологии. 2013. № 7. C.98-100.

- 4. Букварев Е.А., Букварева Т.В., Кузин А.А. Конструктивное исполнение интегрированного модуля цифровой обработки сигналов. // Датчики и системы. 2014. № 11. С.23-27.

### ИНФОРМАЦИЯ

### 17-я Международная научно-техническая конференция

### «ЦИФРОВАЯ ОБРАБОТКА СИГНАЛОВ И ЕЁ ПРИМЕНЕНИЕ - DSPA'2015»

Отвечая целям и задачам консолидации и поддержки отечественных ученых и специалистов, работающих в области передовых информационных технологий реального времени, расширения международных научных связей и содействия внедрению высоких наукоемких технологий XXI века, Российское научно-техническое общество радиотехники, электроники и связи имени А.С. Попова совместно с компанией «AUTEX.Ltd» при поддержке РФФИ и при участии Федерального агентства по промышленности РФ, Министерства образования и науки РФ, Российской секции IEEE Signal Processing Society, Института радиотехники и электроники РАН, Института проблем управления РАН, ЗАО «МНИТИ», МГТУ им. Н.Э. Баумана, МТУСИ, МАИ, МЭИ, РГРТУ и других ведущих российских вузов и организаций, провели 25-27 марта 2015 г. в ИПУ РАН 17-ю Международную научно-техническую конференцию: «Цифровая обработка сигналов и её применение- DSPA'2015». В работе конференции приняли участие свыше 400 человек из 32 городов России и стран СНГ, а также представители ряда стран дальнего зарубежья.

Работа конференции проходила по восьми секциям: «Теория сигналов и систем» (21 доклад, руководители – д.т.н., профессор Ю.С. Шинаков, д.т.н., профессор М.С. Немировский); «Теория и методы цифровой обработки сигналов» (24 доклада, руководители – д.т.н., профессор Ю.А. Брюханов, д.т.н., В.И. Джиган); «Обработка сигналов в системах телекоммуникаций» (17 докладов, руководители – д.т.н., профессор Ю.Н. Прохоров, к.т.н., профессор Санников В.Г.); «Обработка сигналов в радиотехнических системах» (25 докладов, руководители – д.т.н., профессор В.Г. Бартенев, к.т.н., профессор В.С. Сперанский); «Обработка и передача изображений» (40 докладов, руководители – д.т.н., профессор В.В. Дворкович); «Обработка измерительной информации» (11 докладов, руководитель – к.т.н., профессор Ю.В. Скачко); «Проектирование и техническая реализация систем ЦОС» (14 докладов, руководители – д.т.н., профессор В.В. Витязев, к.т.н., доцент В.Б. Стешенко); «Цифровая обработка многомерных сигналов» (12 докладов, руководитель – д.т.н., профессор М.К. Чобану). На конференции было заслушано около 170 докладов, по материалам которых изданы «Труды Конференции» в 2-томах, общим объемом 770 страниц.

В своем приветствии участников конференции Председатель Национального комитета, член-корреспондент РАН Ю.Б. Зубарев, в частности, отметил, что как и в предыдущие годы, начиная с 2000 года, конференция проходит в стенах Института проблем управления РАН, любезно предоставившего нам такую возможность.

Наибольшее число докладов — 35 (в прошлом году было 44 доклада и 56 докладов — 2 года назад) представила Москва (к сожалению, здесь наблюдается явная тенденция к спаду активности московских участников). За ней идут Санкт-Петербург (15 докладов) и Ярославль (14 докладов), стабильно сохраняющие вторую и третью позиции. Несколько сдала свои позиции Рязань (10 докладов), но порадовал Красноярск — 11 докладов. Показательна география участников. Это, помимо большинства городов Центрального региона России, такие регионы и крупные города как: Камчатский край и Владивосток, с одной стороны, и Калининград, с другой стороны, а между ними: Красноярск, Мурманск, Нижний Новгород, Пенза, Ульяновск, Самара, Орел, Смоленск и другие российские города. К сожалению, пока не охвачен Крым. Но, Обществом ведется подготовительная работа в этом направлении.

На пленарном заседании, в день открытия конференции, были заслушаны 4 доклада, в которых нашли отражение вопросы развития современных информационных технологий в области связи и управления, мультимедийных приложений, перспективной элементной базы радиоэлектроники.

В заключительный день работы конференции по каждой секции были подведены общие итоги, а также итоги конкурса на лучшие научные доклады среди молодых ученых и специалистов и состоялось их награждение.